# Universal Chiplet Interconnect Express TM (UCle TM): An open standard for innovations at package level

#### Dr. Debendra Das Sharma

Intel Senior Fellow and Chief Architect of I/O Technology and Standards Intel Corporation

# Agenda

- Introduction to UCIe

- On-Package Interconnects: Opportunities and Challenges

- Universal Chiplet Interconnect Express (UCIe): An Open Standard for Chiplets

- Future Directions and Conclusions

#### 100+ Member Companies and growing!

# Board Members

Leaders in semiconductors, packaging, IP suppliers, foundries, and cloud service providers are joining together to drive

The open chiplet ecosystem.

JOIN US!

### UCIe Consortium is open for membership

- UCIe Consortium welcomes interested companies and institutions to join the organization at the Contributor and Adopter level.

- UCIe was founded in March 2022, incorporated in June 2022. Two levels of memberships: Contributor and Adopter

#### Contributor Membership

- Access the Final Specifications (ex: 1.0, 1.1, 2.0, etc.)

- Implement with the IP protections as outlined in the Agreements

- Right to attend Corporation trade shows or other industry events as determined by the Board

- Participate in the technical working groups

- Influence the direction of the technology

- Access the intermediate (dot level) specifications

- Election to get to the Promoter Class/ Board every year when the term of half the board completes

#### Adopter Membership

- Access the Final Specifications (ex: 1.0, 1.1, 2.0, etc.), but not intermediate level specifications

- Implement with the IP protections as outlined in the Agreements

- Right to attend Corporation trade shows or other industry events as determined by the Board

# Agenda

- Introduction to UCle

- On-Package Interconnects: Opportunities and Challenges

- Universal Chiplet Interconnect Express (UCIe): An Open Standard for Chiplets

- Future Directions and Conclusions

# Moore Predicted "Day of Reckoning"

"It may prove to be more economical to build large systems out of smaller functions, which are separately packaged and interconnected."

-Gordon E. Moore

Example of the components on to integrated circuits. Electronics, Volume 38, Number 8, April 19, 1965.

# Drivers for On-Package Chiplets

- Reticle Limit, yield optimization, scalable performance

- Same dies on package (Scale-up)

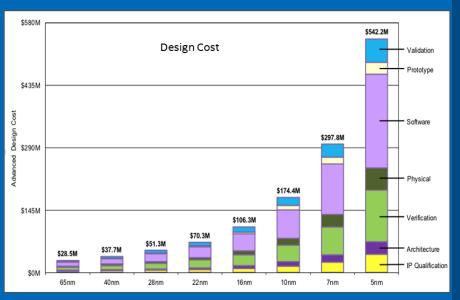

- Increasing design costs at leading edge process nodes

- Die-disaggregated dies across different nodes

- Use new process node for advanced functionality

- Time to Market (Late binding)

- Custom silicon for different customers leveraging a base product

- E.g., Different acceleration functions with common compute

- Different process nodes optimized for different functions

- E.g., Memory, logic, analog, co-packaged optics

- High power-efficient bandwidth with low-latency access (e.g., HBM memory)

Source: IBS (as cited in IEEE Heterogeneous Integration Roadmap)

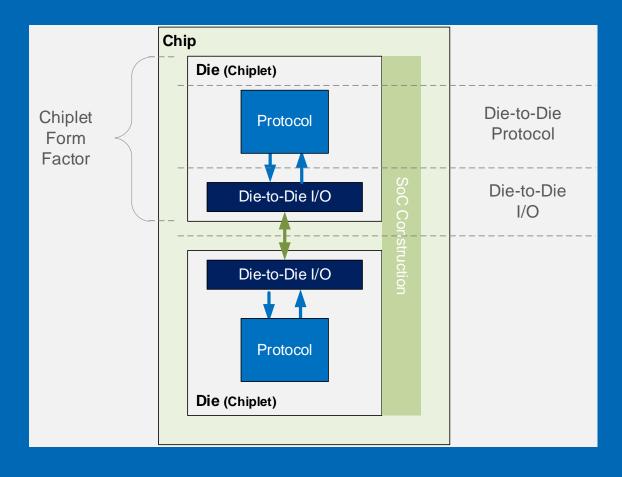

## Components of Chiplet Interoperability

#### Chiplet Form Factor

- Die size

- Bump location

- Power delivery

- Thermal characteristics

- SoC Construction (Application Layer)

- SoC Reset

- Initialization (e.g., fuses)

- Register access

- Security

- Die-to-Die Protocols (Data Link to Transaction Layer)

- Link Layer, transaction Layer, etc.: PCle/CXL/Raw/....

- Internal Interface standardization for plug and play IPs

- Die-to-Die I/O (Physical Layer)

- Bump arrangement and characteristics

- Electrical & thermal characteristics

- Substrate or interposer characteristics

- Length budget, pJ/bit, bit error rate, ...

- Reset, clocking, initialization, and data transfer

- Test and repair

- Technology transition -> multiple bump arrangement/ frequency

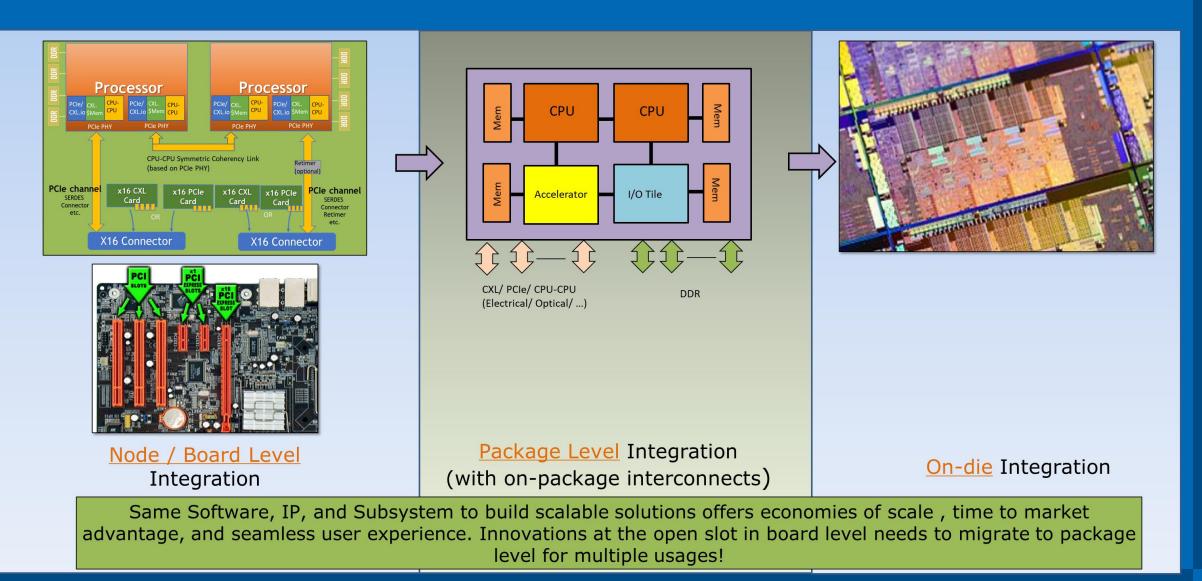

# Design Choice: Seamless Integration from Node → Package → On-die enables Reuse, Better User Experience

HPCA HiPChips Workshop 2023 intel.

# Universal Chiplet Interconnect Express (UCIe):

An Open Standard for Chiplets

#### Guiding principles of UCIe

- 1. Open Ecosystem with Plug-and-play

- 2. Backward compatible evolution when appropriate to ensure investment protection

- 3. Best power, performance, and cost metrics across the industry applicable across the entire compute continuum

- 4. Continuously innovate to meet the needs of evolving compute landscape

(Leveraging decades of experience driving successful industry standards at the board level: PCIe, CXL, USB, etc.)

### Motivation for UCle

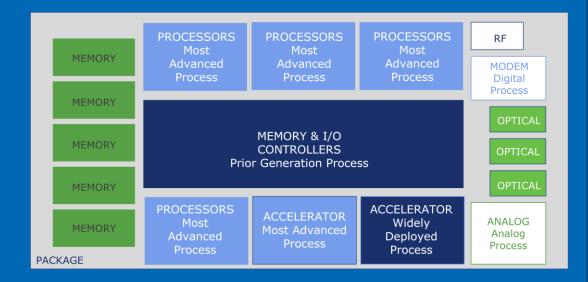

#### OPEN CHIPLET: PLATFORM ON A PACKAGE High-Speed Standardized Chip-to-Chip Interface (UCIe) 20X I/O Performance at 1/20th Power vs off-package SerDes at Launch Gap more prominent with Customer IP & better on-package **Customized Chiplets** technologies in future Sea of Cores (heterogeneous) Memory Advanced 2D/2.5D/3D **Packaging** Heterogeneous Integration Fueled by an Open Chiplet Ecosystem (Mix-and-match chiplets from different process nodes / fabs / companies / assembly)

Align Industry around an open platform to enable chiplet based solutions

- Enables SoC construction that exceeds maximum reticle size

- Package becomes new System-on-a-Chip (SoC) with same dies (Scale Up)

- Reduces time-to-solution (e.g., enables die reuse)

- Lowers portfolio cost (product & project)

- Enables optimal process technologies

- Smaller (better yield)

- Reduces IP porting costs

- Lowers product SKU cost

- Enables a customizable, standard-based product for specific use cases (bespoke solutions)

- Scales innovation (manufacturing/ process locked IPs)

HPCA HiPChips Workshop 2023 intel

# UCle: Key Metrics and Adoption Criteria

#### **Key Performance Indicators**

- Bandwidth density (linear & area)

- Data Rate & Bump Pitch

- Energy Efficiency (pJ/b)

- Scalable energy consumption

- Low idle power (entry/exit time)

- Latency (end-to-end: Tx+Rx)

- Channel Reach

- Technology, frequency, & BER

- Reliability & Availability

- Cost: Standard vs advanced packaging

#### Factors Affecting Wide Adoption

- Interoperability

- Full-stack, plug-and-play with existing s/w

- Different usages/segments ubiquity

- Technology

- Across process nodes & packaging options

- Power delivery & cooling

- Repair strategy (failure/yield improvement)

- Debug controllability & observability

- Broad industry support / Open ecosystem

- Learnings from other standards efforts

UCIe is architected and specified from the ground-up to deliver the best KPIs while meeting wide adoption criteria

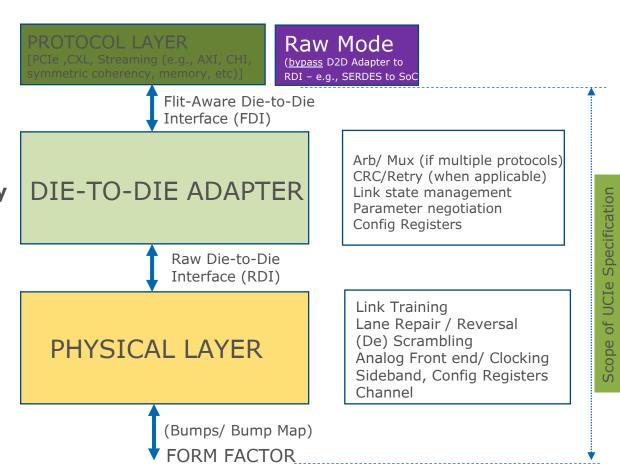

## UCIe 1.0 Specification

- Layered Approach with industry-leading KPIs

- Physical Layer: Die-to-Die I/O

- Die to Die Adapter: Reliable delivery

- Support for multiple protocols: bypassed in raw mode

- Protocol: CXL/PCIe and Streaming

- CXL™/PCIe® for volume attach and plug-and-play

- SoC construction issues are addressed w/ CXL/PCIe

- CXL/PCIe addresses common use cases

- I/O attach, Memory, Accelerator

- Streaming for other protocols

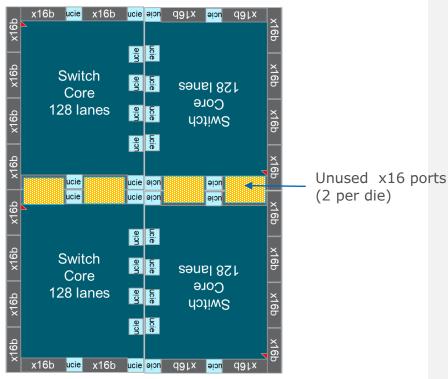

- Scale-up (e.g., CPU/ GP-GPU/Switch from smaller dies)

- Protocol can be anything (e.g., AXI/CHI/SFI/CPI/ etc)

- Well defined specification: interoperability and future evolution

- Configuration register for discovery and run-time

- control and status reporting in each layer

- transparent to existing drivers

- Form-factor and Management

- Compliance for interoperability

- Plug-and-play IPs with RDI/ FDI interface

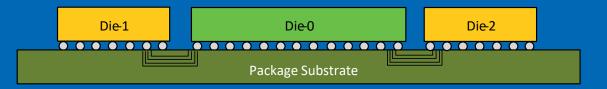

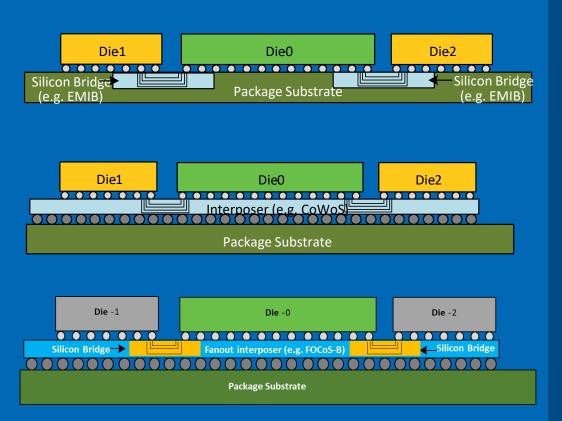

# UCle 1.0: Supports Standard and Advanced Packages

(Standard Package)

Standard Package: 2D – cost effective, longer distance

Advanced Package: 2.5D – power-efficient, high bandwidth density

Dies can be manufactured anywhere and assembled anywhere – can mix 2D and 2.5D in same package – Flexibility for SoC designer

(Multiple Advanced Package Options)

One UCIe 1.0 Spec covers both type of packaging options

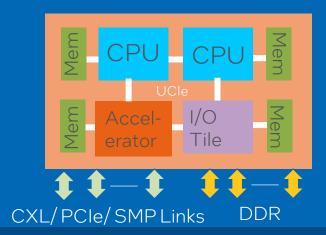

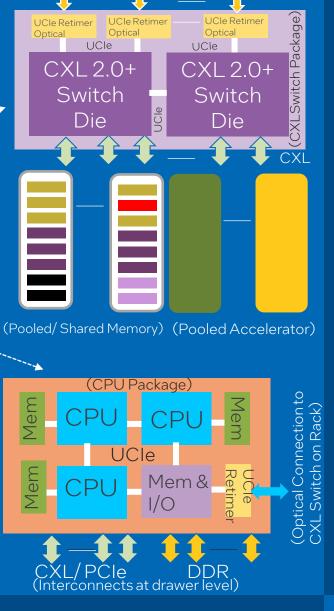

# UCIe Usage Model: SoC at Package Level

- SoC as a Package level construct

- Standard and/ or Advanced package

- Homogeneous and/or heterogeneous chiplets

- Mix and match chiplets from multiple suppliers

- Across segments: Hand-held, Client,

Server, Workstation, Comms, HPC, etc

- Similar to PCIe/ CXL at board level

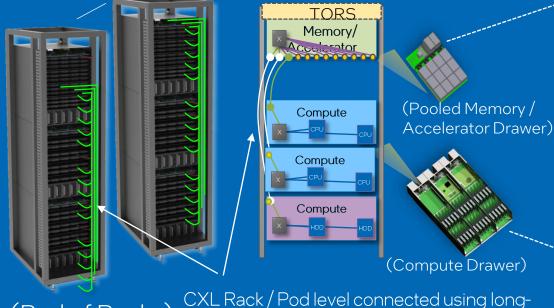

- Need large radix CXL switches challenges: reticle limit, cost, etc.

- UCIe based Chiplets should help with scalable products

- 64G Gen6 x16b CXL links

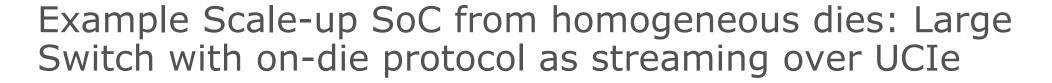

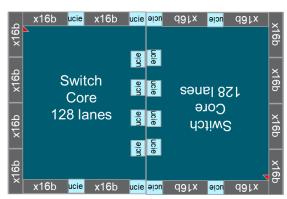

- UCIe as d2d interconnect while this is a scale-up CXL switch, a switch vendor may prefer to have their on-die interconnect protocol be transported over UCIe rather than create a hierarchy of switches which will not work for CXL 2.0 tree-based topology

Medium-sized CXL Switch (256 lanes)

Large CXL switch (512 lanes)

One can construct CPUs (low, medium, large core-count CPUs) from smaller dies connected through UCIe using the same principle

Here the UCIe PHY and D2D adapter will carry the packetized version of internal CPU interconnect fabric

Ack: Nathan Kalyanasundaram

# Example Scale-up Package using Streaming and open-plug-in using PCIe/CXL

Ack: Marvin Denman, Bruce Mathewson, Francisco Socal, Durgesh Srivastava, Dong Wei

(or CHI if both support it)

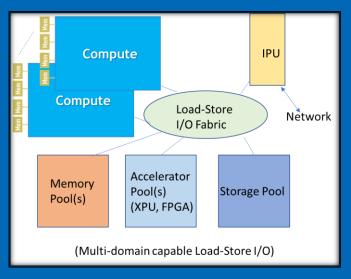

#### UCle Usage: Off-Package Connectivity with UCle Retimers

(Vision: Load-Store I/O (CXL) as the fabric across the Pod providing low-latency and high bandwidth resource pooling/sharing as well as message passing)

(Physical Connectivity using UCIe-Retimer based co-packaged optics)

reach media (Electrical/Optical/..) through

UCle Retimers (e.g., co-packaged optics)

Rack/Pod Level resource pooling/sharing with UCIe

(Pod of Racks)

(Optical connections: Intra-Rack and Pod)

intel

### UCIe 1.0: Characteristics and Key Metrics

| CHARACTERISTICS      | STANDARD<br>PACKAGE  | ADVANCED<br>PACKAGE | COMMENTS                                                                |

|----------------------|----------------------|---------------------|-------------------------------------------------------------------------|

| Data Rate (GT/s)     | 4, 8, 12, 16, 24, 32 |                     | Lower speeds must be supported -interop (e.g., 4, 8, 12 for 12G device) |

| Width (each cluster) | 16                   | 64                  | Width degradation in Standard, spare lanes in Advanced                  |

| Bump Pitch (um)      | 100 - 130            | 25 - 55             | Interoperate across bump pitches in each package type across nodes      |

| Channel Reach (mm)   | <= 25                | <=2                 |                                                                         |

| KPIs / TARGET FOR KEY METRICS  | STANDARD<br>PACKAGE            | ADVANCED<br>PACKAGE | COMMENTS                                                                                 |

|--------------------------------|--------------------------------|---------------------|------------------------------------------------------------------------------------------|

| B/W Shoreline (GB/s/mm)        | 28 - 224                       | 165 - 1317          | Conservatively estimated: AP: 45u; Standard: 110u; Proportionate to data rate (4G - 32G) |

| B/W Density (GB/s/mm²)         | 22-125                         | 188-1350            |                                                                                          |

| Power Efficiency target (pJ/b) | 0.5                            | 0.25                |                                                                                          |

| Low-power entry/exit latency   | 0.5ns <=16G, 0.5-1ns >=24G     |                     | Power savings estimated at >= 85%                                                        |

| Latency (Tx + Rx)              | < 2ns                          |                     | Includes D2D Adapter and PHY (FDI to bump and back)                                      |

| Reliability (FIT)              | 0 < FIT (Failure In Time) << 1 |                     | FIT: #failures in a billion hours (expecting ~1E-10) w/ UCIe Flit Mode                   |

UCIe 1.0 delivers the best KPIs while meeting the projected needs for the next 5-6 years. Wide industry leader adoption spanning semiconductor, manufacturing, assembly, & cloud segments.

# Ingredients of broad inter-operable chiplet ecosystem

**Broad Market** Manufacturing, Packaging and Test

Chiplets & **Chiplet Based Product Attach Points**

Thriving Chiplet Ecosystem

IPs, VIPs, Tools, and Methodologies

Die-to-Die Open Industry Standards w/ compelling KPIs across wide usages

Die-to-Die

Well-defined Specs

(Electrical, Logical, Protocol (e.g., PCIe/CXL) Software, Form-Factor. Management)

Test criteria based on Specs

(Test Definitions. Pass/Fail Criteria: Electrical, Logical, Protocol, Software)

Test H/W & S/W Validates

**And Procedures**

Test criteria

- Compliance

- Interoperability

20

Predictable path to design compliance with UCIe

intel HPCA HiPChips Workshop 2023

#### Future Directions and Conclusions

Chiplets and D2D interface are essential to the compute continuum

Power-efficient performance, yield optimization, different functions, custom solutions, cost-effective

UCIe standardization will propel the development an open ecosystem

- Open plug-and-play "slot" at package level will unleash innovations

- Evolution needs to track the underlying packaging technology to deliver compelling metrics

- Form-factor, New Protocols, and manageability are some other areas for innovation

The open chiplet journey with UCIe just started! Join us in what will be an exciting journey for decades!